产品概述

大发黄金版手机网页版登录按照计算机组成原理最新教学大纲和考研要求精心研发设计的,使得计算机组成原理及计算机系统结构课程变得好教好学,是国内计算机教学领域的旗帜性产品,深得广大高校计算机专业师生的喜爱。对于以往各种产品来说,系统具有更为独特的优点:

1.采用了更为先进的计算机部件电路单元,以及更为先进的计算机整机结构设计,可使学生对计算机组成的完整结构和工作原理具有全面和清晰的认识。

2.为计算机各组成部件和多种结构的模型机实验都配有数据通路图实时图形调试界面,并都具有单拍、单周期、连续等调试功能,使原来难教难学的教学内容变得非常容易理解和掌握;通路图的调试过程还具有保存和回放功能,因而具有更为优秀的教学效果。

(1)先进部件调试手段

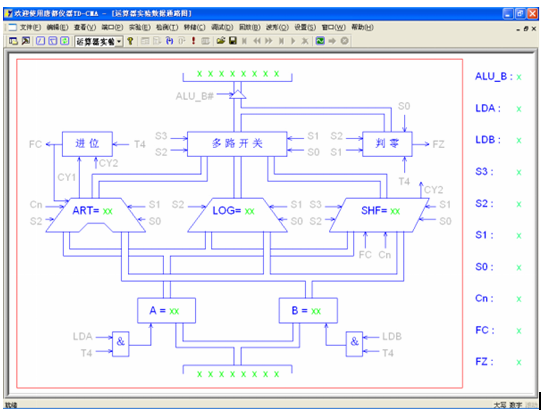

系统为各计算机部件(运算器、存储器、控制器)分别提供了实时动态图形调试工具,使得学生可以轻松了解复杂部件的内部结构和操作方法,并可实时跟踪部件的工作状态

功能特点

1.完整丰富的教学实验内容,确保实验室建设的先进性

在计算机组成原理方面提供了运算器、控制器、存储器、系统总线及总线接口设计等各部件教学实验内容,还提供了简单模型机和复杂模型机的整机实验,以及输入、输出系统方面的实验,特别是提供了具有中断处理功能的模型计算机设计和具有DMA处理功能的模型计算机设计等实验,可使学生对计算机的结构和原理能有一个完整的认识和掌握。

在计算机系统结构方面,通过复杂指令模型机、精简指令模型机、重叠结构模型机和流水结构模型机的实验,可使学生学习并掌握当前各种先进计算机结构的原理及设计。

2.先进的计算机部件设计

运算器部件由一片CPLD来实现,内含算术、逻辑和移位三个运算部件,其中移位运算采用桶形移位器,各部件独立并行工作,并提供了Cache高速缓存控制器设计实验。

3.开放的控制器部件设计

微程序控制器部件由微程序存储器,微命令寄存器,微地址寄存器,微命令译码器,编程电路等构成,其微指令格式和微指令定义可由用户自行设计确定。也可以使用CPLD构造组合逻辑控制器,实现计算机硬布线控制器的设计。

4.先进的系统总线和总线接口设计

系统提供了先进的系统总线结构,与主流的80x86微机具有类似的系统总线和总线接口设计。实验构建的模型计算机总线接口信号,除数据总线、地址总线外,其控制总线是需要根据计算机功能的要求来设计的,具有中断信号线,DMA控制信号线,存储器读写信号线和输入输出读写信号线等,由此便可以开展关于计算机总线接口的设计实验。如:基本输入输出功能的总线接口设计实验、具有中断控制功能和DMA控制功能的总线接口设计实验等。

5.更为灵活、更为实用的时序发生电路和操作台设计

系统提供的时序发生器其机器周期可以在2节拍和4节拍之间选择,这为实验教学提供了更大的灵活性;系统的本地操作控制台也是全新的设计,使得系统在独立使用时,操作起来更为合理、更为方便和实用。

6.先进的实时动态图形调试方式,使学生更容易学懂计算机组成原理

(1)先进部件调试手段

系统为各计算机部件(运算器、存储器、控制器)分别提供了实时动态图形调试工具,使得学生可以轻松了解复杂部件的内部结构和操作方法,并可实时跟踪部件的工作状态。

(2)多种结构模型机调试手段

在模型计算机整机调试的图形调试工具方面,系统提供了简单模型机、复杂模型机、精简指令结构模型机、重叠结构模型机、流水结构模型机的实时动态通路图调试界面。

对简单模型机和复杂模型机还提供了动态微程序流程图,将微程序的运行过程可实时动态的表现出来,使用户可以从微程序的角度观察计算机指令运行的过程并对系统进行调试。

实验内容

1.运算器及设计实验

(1)基本运算器实验

(2)超前进位加法器设计实验

(3)阵列乘法器设计实验

2.存储系统及设计实验

(1)静态随机存储器实验

(2)Cache控制器设计实验

3.控制器及设计实验

(1)时序发生器设计实验

(2)微程序控制器实验

4.系统总线与总线接口实验

(1)系统总线和具有基本输入输出功能的总线接口实验

(2)具有中断控制功能的总线接口设计

(3)具有DMA控制功能的总线接口设计

5.模型计算机的设计实验

(1)CPU与简单模型机设计实验

(2)硬布线控制器模型机设计实验

(3)复杂模型机设计实验

6.输入、输出系统实验

(1)具有中断处理功能的模型计算机设计实验

(2)具有DMA处理功能的模型计算机设计实验

(3)典型I/O接口8253扩展设计实验

7.先进计算机结构的设计及研究实验

(1)基于RISC处理器的模型计算机设计实验

(2)基于重叠技术的模型计算机设计实验

(3)基于流水技术的模型计算机设计实验

符合招标文件部分:

工作温度:-10℃~+40℃;电源要求:220V,50Hz。

1. 基本技术

(1) 采用 FPGA-A7,FPGA 可直接提供内存控制器,支持 VIVADO 开发工具;

(2) 配置1GbDDR3 标准内存;

(3) 配置高速缓存控制器,算术运算、逻辑运算等独立并行工作部件;

(4) 配置串口,运算器,存储器,控制器等及各部件等动态图形调试用的显示屏;

(5) 配置以太网接口 RJ-45,10/100M 自适应;

(6) 配置基本的输入输出设备、usb、LED 灯、数码管、拨码开关、矩阵按键、 串口等;

(7) 配置完整的教学实验指导书(教师版和学生版);提供《数字逻辑》教 学实验指导书;《计算机组成原理》教学实验指导书;《计算机体系结构》 教学实验指导书;《操作系统》教学实验指导书;《CPU 设计》教学实验指 导书各一套;投标现场提供指导书样品各一本;

2 实验要求

(1)重点实验 实验一 数据运算:定点加法 实验二 数据运算:乘法器 实验三 寄存器堆实现 实验四 ALU 模块实现 实验五 存储器 实验六 单周期 CPU 实现 实验七 多周期 CPU 实现 课程设计 静态流水 CPU 实现

(2)基础实验 实验一 组合逻辑电路实验 实验二 锁存器、时钟与触发器电路实验 实验三 时序逻辑电路实验 实验四 存储器实验等